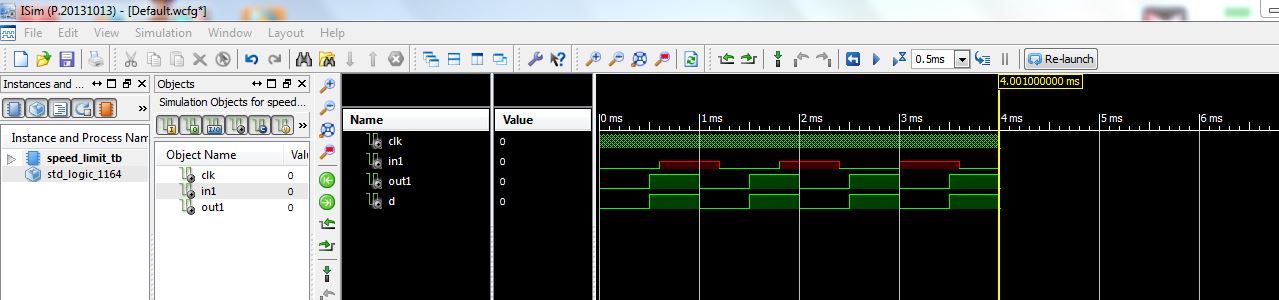

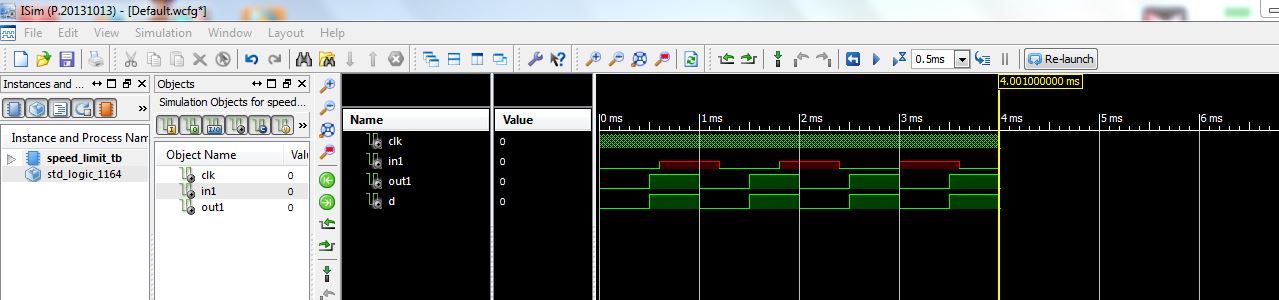

این کد زیری قراره این کارو بکنه: پالسی که در ورودی می گیره اگر دوره تناوبش بیشتر از 1ms بود عینا به خروجی منتقل کنه و اگر دوره تناوب ورودی کمتر از 1ms بود موجی با دوره تناوب 1ms به خروجی بده . برنامه تو سنتز error و warning نمیده اما شبیه سازیش درست نیست یعنی وقتی ورودی با دوره تناوب بیشتر از 1ms تو تست بنچ بهش میدم عینا به خروجی نمیده(زمان یک بودن ورودی ام x می شه!) چرااااااااا؟؟؟؟؟؟؟؟؟؟؟ تست بنچ و کد اصلی و عکس شبیه سازی رو گذاشتم.

[code=vhdl]----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 19 42 06/13/2015

42 06/13/2015

-- Design Name:

-- Module Name: limit_s - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity limit_s is

Port ( in1 : inout STD_LOGIC:='0';

out1 : out STD_LOGIC:='0';

clk : in STD_LOGIC);

end limit_s;

architecture Behavioral of limit_s is

signal d: std_logic:='0';

signal flag: std_logic:='0';

signal cnt : integer range 0 to 50000;

signal cnt1 : integer range 0 to 25000;

begin

process(clk)

begin

if (rising_edge(clk))then

cnt1<=cnt1+1;

if (cnt1=25000)then

cnt1<=0;

d<=not d;

end if;

if (in1='1' then

then

cnt<=cnt+1;

if(cnt>=25000)then

flag<='1';

else

flag<='0';

end if;

end if;

end if;

end process;

process(clk)

begin

if (rising_edge(clk))then

if (flag='1' then

then

out1<=in1;

else

out1<=d;

end if;

end if;

end process;

end Behavioral;

[/code]

و تست بنچ:

[code=vhdl]--------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 23:32:23 06/13/2015

-- Design Name:

-- Module Name: D:/ISE_PROJECTS/speed_limit/speed_limit_tb.vhd

-- Project Name: speed_limit

-- Target Device:

-- Tool versions:

-- Description:

--

-- VHDL Test Bench Created by ISE for module: limit_s

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

-- Notes:

-- This testbench has been automatically generated using types std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O of a design in order

-- to guarantee that the testbench will bind correctly to the post-implementation

-- simulation model.

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY speed_limit_tb IS

END speed_limit_tb;

ARCHITECTURE behavior OF speed_limit_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT limit_s

PORT(

in1 : INOUT std_logic:='0';

out1 : OUT std_logic;

clk : IN std_logic

);

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

--BiDirs

signal in1 : std_logic;

signal out1 : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: limit_s PORT MAP (

in1 => in1,

out1 => out1,

clk => clk

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for 10 ns;

clk <= '1';

wait for 10 ns;

end process;

process

begin

in1 <= '0';

wait for 0.6 ms;

in1 <= '1';

wait for 0.6 ms;

end process;

END;

[/code]

[code=vhdl]----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 19

42 06/13/2015

42 06/13/2015 -- Design Name:

-- Module Name: limit_s - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity limit_s is

Port ( in1 : inout STD_LOGIC:='0';

out1 : out STD_LOGIC:='0';

clk : in STD_LOGIC);

end limit_s;

architecture Behavioral of limit_s is

signal d: std_logic:='0';

signal flag: std_logic:='0';

signal cnt : integer range 0 to 50000;

signal cnt1 : integer range 0 to 25000;

begin

process(clk)

begin

if (rising_edge(clk))then

cnt1<=cnt1+1;

if (cnt1=25000)then

cnt1<=0;

d<=not d;

end if;

if (in1='1'

then

thencnt<=cnt+1;

if(cnt>=25000)then

flag<='1';

else

flag<='0';

end if;

end if;

end if;

end process;

process(clk)

begin

if (rising_edge(clk))then

if (flag='1'

then

thenout1<=in1;

else

out1<=d;

end if;

end if;

end process;

end Behavioral;

[/code]

و تست بنچ:

[code=vhdl]--------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 23:32:23 06/13/2015

-- Design Name:

-- Module Name: D:/ISE_PROJECTS/speed_limit/speed_limit_tb.vhd

-- Project Name: speed_limit

-- Target Device:

-- Tool versions:

-- Description:

--

-- VHDL Test Bench Created by ISE for module: limit_s

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

-- Notes:

-- This testbench has been automatically generated using types std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O of a design in order

-- to guarantee that the testbench will bind correctly to the post-implementation

-- simulation model.

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY speed_limit_tb IS

END speed_limit_tb;

ARCHITECTURE behavior OF speed_limit_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT limit_s

PORT(

in1 : INOUT std_logic:='0';

out1 : OUT std_logic;

clk : IN std_logic

);

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

--BiDirs

signal in1 : std_logic;

signal out1 : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: limit_s PORT MAP (

in1 => in1,

out1 => out1,

clk => clk

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for 10 ns;

clk <= '1';

wait for 10 ns;

end process;

process

begin

in1 <= '0';

wait for 0.6 ms;

in1 <= '1';

wait for 0.6 ms;

end process;

END;

[/code]

oo: :redface: چه کار می شود کرد ؟؟؟

oo: :redface: چه کار می شود کرد ؟؟؟

دیدگاه