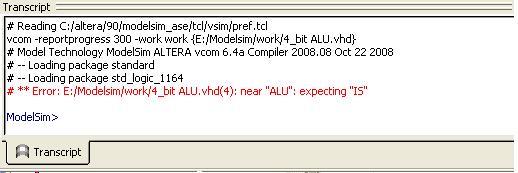

دوستان به نظر شما اشکال این برنامه 4bit ALU چیه؟؟؟

کد:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity bit ALU is

port(

A : in std_logic_vector(3 downto 0);

B : in std_logic_vector(3 downto 0);

c_in: in std_logic_vector;

s : in std_logic_vector(1 downto 0);

Y : out std_logic_vector (3 downto 0);

);

end bit ALU;

architecture arch of bit ALU is

signal sg1,sg2,sg3,sg4:std_logic_vector(3 downto 0);

begin

for k in 0 to 3 loop

sg1(k)<=((A(k) xor B(k))xor c_in);

c_in<=(A(k) and B(k))or((A(k) xor B(k))and C_in)

end loop

sg2<=A xor B;

sg3<= A and B;

sg4<=A or B;

Y<= sg1 WHEN S(1)='0' AND S(0)='0' ELSE

sg2 WHEN S(1)='0' AND S(0)='1' ELSE

sg3 WHEN S(1)='1' AND S(0)='0' ELSE

sg4 WHEN S(1)='1' AND S(0)='1' ;

end bit ALU;

دیدگاه