سلام

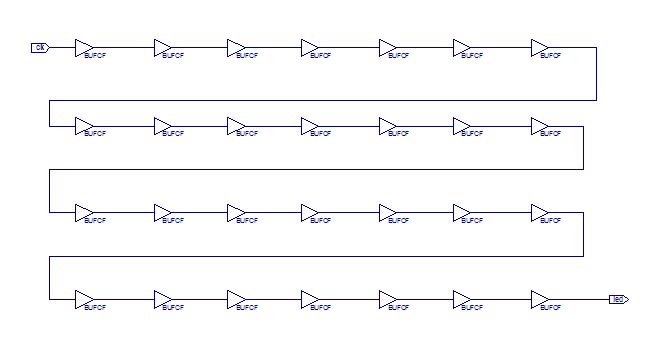

توی یه برنامه ای نیاز دارم که لبه بالا رونده یه کلاک رو با یه تاخیر تقریبی 1 نانو ثانیه به یه قسمت دیگه از برنامه اعمال کنم .از روی دیتاشیت ( xc3s50an ) چطوری میشه فهمید که مقدار تاخیر انتشار یه گیت بافر که داخل fpga تشکیل میشه تقریبا چقدر هست؟

توی یه برنامه ای نیاز دارم که لبه بالا رونده یه کلاک رو با یه تاخیر تقریبی 1 نانو ثانیه به یه قسمت دیگه از برنامه اعمال کنم .از روی دیتاشیت ( xc3s50an ) چطوری میشه فهمید که مقدار تاخیر انتشار یه گیت بافر که داخل fpga تشکیل میشه تقریبا چقدر هست؟

دیدگاه